本文最后更新于284 天前,其中的信息可能已经过时,如有错误请发送邮件到82872443@qq.com

📌引脚功能

1. COMP

内部误差放大器的输出端。外接RC网络到地,用于补偿和稳定反馈环路,是决定电源动态响应和稳定性的关键。

2. VFB

误差放大器的反相输入端。通过分压电阻对输出电压进行采样,与内部2.5V基准比较,产生误差信号以调节脉宽,实现稳压。

3. ISENSE

连接到功率管下方的采样电阻,用于检测主开关电流。当其电压达到1V阈值时,会立即关断当周期的脉冲,实现逐周期电流限制。

4. RT/CT

外接电阻 RT 和电容 CT,用于设定内部振荡器的工作频率。开关频率的计算公式为:fc≈1.72/RT×CT。

5. GND

芯片的信号与功率参考地。

6. OUT

PWM驱动信号输出端。通常采用图腾柱结构,具备强大的灌/拉电流能力,可快速、高效地驱动外部功率MOSFET。

7. VCC

芯片的工作电源。具备关键的欠压锁定 (UVLO) 功能,其启动电压为16V,关闭电压为10V,以确保芯片只在安全的电压范围内工作。

8. VREF

提供一个精确的 +5V 基准电压,为 RT/CT 网络和反馈电路提供稳定可靠的电源参考。

⚙️ 工作流程

🚀 启动过程

- 上电与VCC充电: 当AC输入经整流滤波后,高压直流电通过一个大阻值的启动电阻(如300kΩ),开始为VCC引脚外的滤波电容

C_VCC缓慢充电。此时芯片处于待机状态,启动电流极低(<1mA)。 - 欠压锁定 (UVLO) 与唤醒: UC3842内置了带有迟滞功能的欠压锁定(Under-Voltage Lockout)电路,这是保证芯片稳定工作的关键。

- 唤醒阈值

V_ON: 当C_VCC上的电压缓慢爬升至 16V 时,达到UVLO的开启阈值。此时UVLO电路动作,解除锁定,芯片被“唤醒”。 - 关断阈值

V_OFF: 如果VCC电压跌落至 10V,芯片会再次进入锁定状态,停止工作。 - 迟滞窗口: 16V开启、10V关闭的这个6V电压差,有效防止了VCC电压在阈值点附近波动而引起的芯片反复启停。

- 唤醒阈值

- 芯片启动与控制权交接: 一旦UVLO解除,芯片立即进入正常工作状态:

VREF建立: 内部5V基准电压VREF迅速建立并稳定输出。- 振荡器工作:

RT/CT引脚配置的振荡器开始工作,产生时钟信号。 - 首次脉冲:

OUTPUT引脚输出第一串PWM脉冲,驱动MOSFET开始开关动作。

- 辅助绕组接管供电: MOSFET工作后,变压器开始传输能量,其辅助绕组上产生的感应电压经二极管整流和电容滤波后,会为VCC提供一个稳定(通常在12V-15V之间)且高效的持续供电。此时,功率消耗较大的启动电阻的使命基本完成,辅助绕组正式“接管”芯片的供电任务。

注意: 如果VCC电容

C_VCC的容值选取过小,可能会出现在辅助绕组还未建立稳定供电前,C_VCC的电压就已从16V跌落至10V以下的情况。这会导致芯片关断、重新充电、再次启动……如此往复,形成“打嗝”现象。

⚡️ 电流内环

- 周期开始: 每个开关周期的起点,由内部振荡器置位PWM锁存器,

OUTPUT输出高电平,外部MOSFET导通。 - 电流爬升与采样: MOSFET导通后,变压器初级绕组的电流从零开始线性增加。这个电流流过与MOSFET源极串联的电流采样电阻

R_SENSE,在其上产生一个与电流成正比的、线性上升的电压斜坡V_ISENSE。 - 电流比较与关断:

V_ISENSE的电压被实时送入内部电流比较器的同相输入端,与来自电压外环的误差电压V_COMP(经过内部处理后的值)在反相输入端进行比较。- 一旦

V_ISENSE的电压追上并超过V_COMP所设定的阈值,电流比较器立即翻转,复位PWM锁存器。

- 一旦

- 周期结束: PWM锁存器被复位后,

OUTPUT引脚立即变为低电平,MOSFET关断,初级电流截断。MOSFET将保持关断,直到下一个时钟周期到来,重复此过程。 - 峰值限流保护:

ISENSE引脚内部还有一个固定的 1V 硬件保护阈值。无论V_COMP电压有多高,只要V_ISENSE电压触及1V,PWM周期将立即被终止。这提供了一个极为可靠的、逐周期生效的硬件过流保护,有效防止了变压器饱和和MOSFET损坏。采样电阻R_SENSE的值通常由最大峰值电流决定:

$$

R_{SENSE} = \frac{1V}{I_{peak(max)}}

$$

🌍 电压外环

- 输出采样: 在电源的次级(输出侧),通常使用一个精密基准源(如 TL431)来精确采样输出电压。

- 误差隔离与传递: 采样到的电压与TL431的内部基准比较后,驱动一个光电耦合器。光耦的作用是在电气隔离的前提下,将输出电压的误差信号传递回初级侧。

- 脉宽调节 (两种经典方式): 光耦在初级侧通过调节内部误差放大器(E/A)的状态,最终改变

COMP引脚的电压。根据电路设计的不同,主要有两种反馈方式:- 方式一:反馈至 VFB,控制误差放大器 (最常用)

- 电路结构: 这是最经典的应用方式。光耦的输出端连接到

VFB引脚(误差放大器的反相输入端)。VFB通过电阻网络与VREF和光耦相连。 - 工作原理: 误差放大器(E/A)将

VFB引脚的电压与内部 2.5V 的基准电压进行比较,其输出就是COMP引脚的电压。- 当输出电压

V_out偏高时: TL431导通增强 → 光耦电流增大 →VFB电压被拉低 → 误差放大器使得COMP电压降低。 - 当输出电压

V_out偏低时: TL431导通减弱 → 光耦电流减小 →VFB电压升高 → 误差放大器使得COMP电压升高。

- 当输出电压

- 电路结构: 这是最经典的应用方式。光耦的输出端连接到

- 方式二:直接控制 COMP 引脚

- 电路结构: 在这种方式下,

VFB引脚直接接地或接固定偏置,使其不起作用。光耦的集电极则直接连接到COMP引脚。 - 工作原理:

COMP引脚内部有一个上拉电流源。光耦的导通程度直接决定了从COMP引脚“吸走”多少电流,从而直接控制其电压高低。- 当输出电压

V_out偏高时: 光耦导通增强,直接将COMP引脚的电压拉低。 - 当输出电压

V_out偏低时: 光耦导通减弱,COMP引脚的电压在其内部电流源作用下升高。

- 当输出电压

- 电路结构: 在这种方式下,

COMP电压来调节PWM占空比。一个更低的COMP电压意味着V_ISENSE上的电流斜坡只需爬升到一个更低的值就能关断MOSFET,从而缩短导通时间(减小占空比),减少能量传输,使输出电压回落至设定值,反之亦然,最终形成一个稳定的闭环控制。 - 方式一:反馈至 VFB,控制误差放大器 (最常用)

| 状态变化 | VFB (Pin 2) | COMP (Pin 1) | 占空比 (D) |

|---|---|---|---|

| 负载减轻 | ↑ | ↓ | ↓ |

| 负载加重 | ↓ | ↑ | ↑ |

🛠️ 调试要点

核心挑战:环路不稳定与电感啸叫

在调试中,最常见也最令人头疼的问题就是环路不稳定,其典型表现为:

- “大小波”现象:PWM占空比在极大和极小值之间剧烈振荡。

- 电感啸叫:不稳定的占空比导致电感电流中含有低频分量,从而产生人耳可闻的噪声。

根本原因在于,UC3842要稳定工作,其内部的PWM比较器必须在每个周期都有一个干净、稳定的斜坡信号进行比较。如果ISENSE引脚的信号质量不佳(例如在BUCK电路中,或噪声干扰严重),PWM生成就会与内部时钟脱节,导致振荡。

关键解决方案:斜坡补偿 (Slope Compensation)

这是解决上述问题的“杀手锏”。尤其是在BUCK、BOOST等拓扑或者占空比大于50%的应用中,斜坡补偿几乎是必需的。

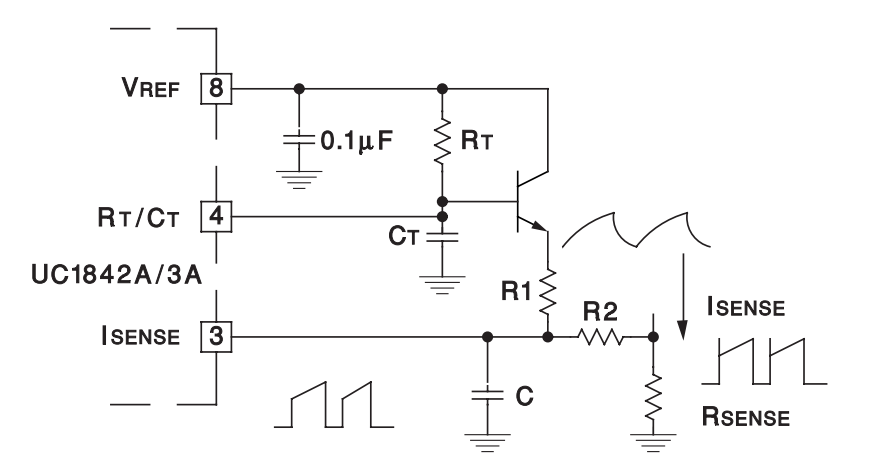

- 操作方法:将振荡器引脚(

RT/CT,引脚4)产生的锯齿波,通过一个电阻电容网络耦合到电流采样引脚(ISENSE,引脚3)。 - 实现原理:

- 强制同步:在原有的电流采样信号上,叠加一个来自振荡器的、纯净的锯齿波斜坡。这确保了PWM比较器每周期都有一个可靠的基准斜坡,使PWM频率与振荡频率严格同步。

- 抑制振荡:这个额外叠加的斜坡可以有效抑制电流模控制固有的次谐波振荡,从而使环路在各种工况下都能保持稳定。

推荐调试流程:先开环,后闭环

- 第一步:开环调试 (验证电流内环)

- 操作:暂时断开电压反馈环,例如将

FB(引脚2)接地。同时,在COMP(引脚1)上外接一个可调直流电源(例如0-5V)。 - 目的:独立验证“电流环路”和“驱动电路”是否工作正常。通过手动调节

COMP引脚的电压,观察输出PWM的占空比是否能从小到大平滑、稳定地变化。如果这一步正常,说明电路的“动力”部分没问题。

- 操作:暂时断开电压反馈环,例如将

- 第二步:闭环调试 (调节电压外环)

- 操作:在开环测试通过后,移除

COMP引脚上的可调电源,恢复FB引脚的反馈网络。 - 目的:开始调节电压环的补偿参数(即1脚和2脚外的RC网络),使输出电压能够精确、稳定地锁定在目标值。

- 操作:在开环测试通过后,移除