关键波形图

一、先锁定最恶劣工况,所有选型都从这里开始

四开关 Buck-Boost 的器件选型不能只看标称功率。

真正决定器件应力的是:最低输入电压、最高输出电压、最大输出电流、最高环境温度、最高开关频率和最差散热条件。

低压输入满载输出时,输入电流和电感电流会非常大;高压工作时,MOSFET 的电压应力、开关损耗和寄生电容相关损耗会显著增加。

如果原项目中用 500W 或 15A 作为示例,它们可以作为计算口径示范;实际 1000W 设计必须把电流、热损耗和电容纹波电流按目标功率重新放大校核。

方法不变,数值不能照抄。

1. 控制器先看拓扑能力和保护能力

控制 IC 要支持同步四开关控制、宽输入输出范围、足够的栅极驱动能力、可靠限流、斜坡补偿、轻载模式和完善保护。以 ISL81601 这类控制器为例,它适合宽压 Buck-Boost 设计,开关频率可设在几百 kHz,用来平衡体积、效率和动态响应。

控制器选型不是只看“能不能升降压”,还要重点确认 Buck、Boost 和 Buck-Boost 过渡区的控制方式是否清楚,限流和斜坡补偿是否覆盖最恶劣工况。否则后面即使功率器件足够强,系统也可能在某些输入输出组合下出现次谐波振荡、轻载啸叫或负载瞬态不稳定。

2. MOSFET 选型要同时看耐压、电流和损耗权衡

MOSFET 不适合只盯某一个参数。比较稳妥的筛选顺序是:先看耐压,再看电流和高温降额,最后看损耗权衡。

先看耐压

若系统最高输入和输出都可能达到 56V,60V MOSFET 的裕量通常偏小,因为大电流开关瞬间 PCB 寄生电感会产生 Vds 尖峰。

工程上通常会选 80V 或 100V MOSFET,并结合实际 Vds/SW 波形确认降额是否足够。

再看电流能力和高温降额

规格书中的连续漏极电流 Id 往往是在理想壳温下给出,实际 100℃ 左右能力会明显下降。

以 500W、12V 输入、效率约 90% 估算,输入平均电流约为:

$$

I_{in}\approx\frac{P_{out}}{V_{in}\times\eta}\approx\frac{500W}{12V\times0.9}\approx46A

$$

加上电感纹波后,峰值电流可能超过 50A。

若功率提升到 1000W,这个电流压力会进一步放大。因此 MOSFET 不能只按平均电流选,通常要同时核对连续电流、高温降额、脉冲电流能力、SOA 和封装热阻。

最后看损耗权衡

300kHz 左右的开关频率下,不能只追求极低 Rds(on)。Rds(on) 很低的 MOSFET 往往 Qg、Coss、Qoss 较大,会带来更高的驱动损耗和开关损耗。

常用 FOM 是:

$$

R_{ds(on)} \times Q_g

$$

驱动损耗可用下式估算:

$$

P_{gate}=Q_g\times V_{gs}\times f_{sw}

$$

所以 MOSFET 的目标不是某一个参数极致,而是在耐压、电流、导通损耗、开关损耗和散热之间取得平衡。

3. 电感要分别计算 Buck 和 Boost 两端工况

四开关 Buck-Boost 的电感选型必须分别计算 Buck 和 Boost 两种极端工况,最后取更严苛的一端。

通常把电感峰峰值纹波电流设为最大平均电感电流的 20% 到 30%。

Buck 模式下的感值公式为:

$$

L_{buck}=\frac{V_{out}\times(V_{in(max)}-V_{out})}{V_{in(max)}\times f_{sw}\times\Delta I_{L_buck}}

$$

Boost 模式下的感值公式为:

$$

L_{boost}=\frac{V_{in(min)}\times(V_{out}-V_{in(min)})}{V_{out}\times f_{sw}\times\Delta I_{L_boost}}

$$

Boost 模式下,电感平均电流近似等于输入电流:

$$

I_{in}\approx\frac{V_{out}\times I_{out}}{V_{in(min)}\times\eta}

$$

因此,低压输入、满载输出通常是电感最危险的工况。

电感校核时重点看四项:Isat 必须高于逐周期限流阈值,Irms 要满足长期温升要求,DCR 越低越有利于降低铜损;对于大功率项目,大尺寸扁平线电感或低 DCR 磁件往往比小体积磁件更现实。

4. 电容选型要区分输入端和输出端的压力来源

输入电容和输出电容不能按同一套直觉选。Buck 模式下,输入电流是不连续脉冲状,输入电容承受较大的 RMS 纹波电流;Boost 模式下,输出电流是不连续脉冲状,输出电容承受较大的 RMS 纹波电流和 ESR/ESL 尖峰。

Boost 主开关导通期间,输出电容需要独立给负载供电,因此输出电容容量可按下式初步估算:

$$

C_{out(min)}=\frac{I_{out(max)}\times D_{max}}{f_{sw}\times\Delta V_{out(limit)}}

$$

这个公式只估算充放电纹波,还要叠加 ESR 阶跃、ESL 尖峰、陶瓷电容直流偏压衰减和布局寄生影响。

实际设计中通常采用大容量电容和高频 MLCC 混搭。0.1uF、1uF、10uF 等高频陶瓷要尽量靠近功率管和热环路。

大电容能补能量,但放远了不能解决尖峰。

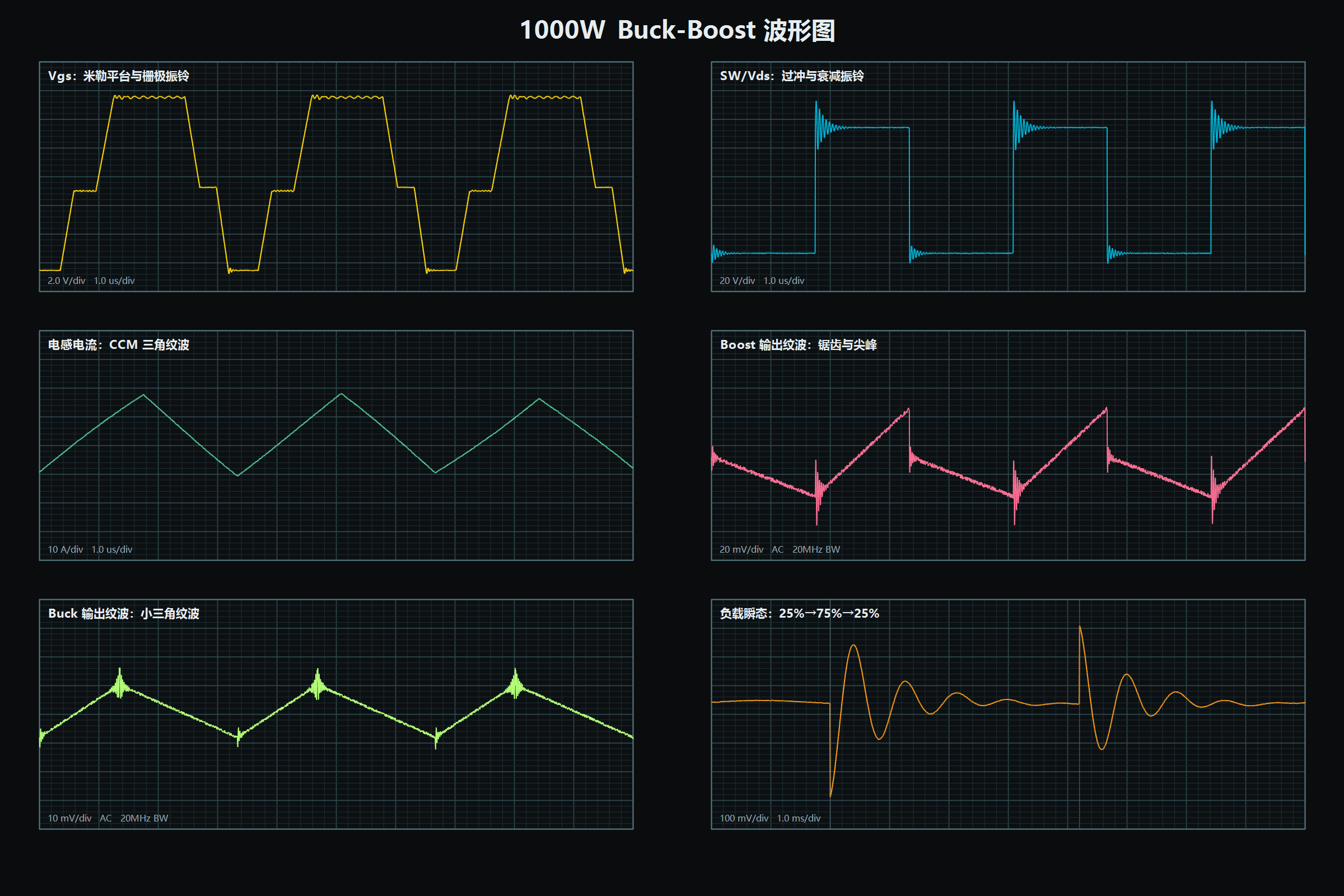

二、用关键波形判断问题来源

器件选型给出了“能不能承受”的基础,波形则告诉我们“实际工作得好不好”。

1000W Buck-Boost 调试时,优先观察五类波形:

| 波形 | 主要对应问题 |

|---|---|

| Vgs | 开关损耗、误导通、驱动稳定性 |

| Vds/SW | 电压应力、振铃、EMI 风险 |

| 电感电流 | 磁件应力、限流、次谐波风险 |

| 输出纹波 | 输出质量、布局和电容有效性 |

| 负载瞬态 | 环路稳定性、动态响应 |

1. 栅极波形 Vgs 决定开关动作

栅极波形直接决定 MOSFET 的开通和关断过程。常见问题有三类。

波形不够陡峭

也就是上升沿或下降沿缓慢。这样会让 MOSFET 在线性区停留更久,开关过程拖长,开关损耗显著增加。

优化方向是减小栅极驱动电阻 Rg,或者更换峰值输出电流更大的栅极驱动芯片。

开通或关断边沿有尖峰

主要原因是 Vds 节点极高的 dv/dt 通过米勒电容 Cgd 耦合到栅极,产生瞬态位移电流。

工程处理方式是采用负压关断来增加抗干扰裕量,或者在 DS 两端增加 RC Snubber,从源头削弱 dv/dt 和振铃。

高电平或低电平期间持续高频振荡

它通常来自驱动回路寄生电感与 MOSFET 输入电容 Ciss 的 LC 谐振。

优化优先级是:先优化 Layout,尽量缩短驱动器到 MOSFET 的走线并减小驱动环路面积;其次适当增大 Rg 增加阻尼;必要时在栅极串联高频磁珠,吸收高频能量。

实际设计中也常用“电阻并联二极管”的不对称驱动网络,独立调节开通和关断阻抗,例如慢开抑制振荡、快关降低损耗。

2. 米勒平台要用正确测法观察

米勒平台是 MOSFET 开关损耗最大的区域。

开通时,当栅极电压升到某一点,漏极电流已经达到较大值,此时漏极电压 Vds 开始快速下降。由于米勒效应,驱动器的电流很大一部分用来给 Cgd 充电,导致 Vgs 短时间停留在平台电压上,直到 Vds 基本降到底部。

测量时要区分低边和高边。低边 MOSFET 的源极接地,用普通探头测 Gate-to-GND 基本等于 Vgs,因此可以看到米勒平台;高边 MOSFET 的源极是剧烈跳变的 SW 节点,如果只测 Gate-to-GND,巨大的共模跳变会掩盖真实的栅源电压变化。

要看高边管真实米勒平台,必须用差分探头紧贴 G、S 两端测量。

缩短米勒平台的思路包括提高驱动能力、合理减小栅极阻抗、降低 Qgd,并通过良好布局减少寄生参数。

负压关断主要用于提高关断抗扰度,避免高 dv/dt 误导通。

3. 开关节点 Vds/SW 反映电压应力和 EMI 风险

开关节点是系统 EMI 和电压应力的主要来源。常见问题是关断瞬间产生高压过冲和高频振荡。

其原因是 MOSFET 快速关断切断电流,极高的 di/dt 激发主功率回路寄生电感,产生感应电压:

$$

V=L\cdot\frac{di}{dt}

$$

随后,寄生电感又会与 MOSFET 输出电容 Coss 等寄生电容形成谐振。

优化策略有三点:第一,最小化高 di/dt 功率回路面积;第二,在 MOSFET 的 D、S 两端并联 RC Snubber,用电容吸收尖峰能量、用电阻耗散振荡能量;第三,适当增大关断侧 Rg,主动降低 di/dt,用少量关断损耗换取过冲降低。

这里要注意顺序:如果 Vds/SW 振铃很严重,先不要急着加很大的吸收网络。应先确认热环路布局、输入输出高频电容位置和测量接地方式。

Snubber 是工程修正手段,不应该替代正确的功率回路布局。

4. 输出纹波要先排除测量噪声

输出纹波是衡量电源性能的核心指标。测量毫伏级纹波时,错误探测方式引入的噪声可能超过真实纹波,导致误判。

正确测量的核心是:最小化探头接地环路面积。

测量时建议开启 AC 耦合,去掉输出电压直流分量,使示波器可以使用较小垂直档位;同时开启 20MHz 带宽限制,滤除与变换器工作无关的超高频环境噪声。推荐使用接地弹簧法,让探针尖端和弹簧地直接跨接在输出电容两端;如果没有接地弹簧,可以用一小段很短的导线做“探针-绕地线”测法。

Buck 模式下的输出纹波

Buck 模式下,电感位于输出端,输出电流是连续的。

输出纹波主要表现为比较干净的三角波或锯齿波,这是电感纹波电流对输出电容周期性充放电形成的。

如果 Buck 输出纹波中的三角波幅度过大,通常说明电感值偏小、输出总电容量不足,或者开关频率设置偏低。

如果叠加明显尖峰和振铃,则更多指向 PCB 布局、输出 MLCC 位置或测量方式问题。

Boost 模式下的输出纹波

Boost 模式下,输出电流是不连续的。

只有主开关关断、续流二极管或同步管导通时,电感电流才脉冲式送到输出端。因此 Boost 输出纹波通常带有陡峭尖峰和阶跃,整体呈锯齿状。

尖峰和阶跃主要来自两类问题:一是输出电容电流突变量作用在 ESR、ESL 上,二是输出侧热环路寄生电感造成振铃。

优化重点是降低输出电容 ESR 和 ESL,增加低 ESR 电容并联数量,并把高频 MLCC 放在离同步管和输出回流路径最近的位置。

5. 电容发热本质上是 RMS 纹波电流问题

电容发热的根本原因是交流纹波电流流经 ESR 产生功耗:

$$

P_{loss}=I_{RMS}^2\times ESR

$$

Buck 模式下,输入电流是不连续脉冲状,因此输入电容 RMS 电流大、发热严重;输出电流相对连续,输出电容发热较轻。

Boost 模式刚好相反,输入电流连续,输入电容压力较小;输出电流不连续,输出电容承受较大 RMS 纹波电流,是主要发热点。

| 模式 | 输入电容 | 输出电容 |

|---|---|---|

| Buck | 电流不连续,RMS 电流大,发热严重 | 电流连续,RMS 电流小,发热轻微 |

| Boost | 电流连续,RMS 电流小,发热轻微 | 电流不连续,RMS 电流大,发热严重 |

6. 电流模式控制还要警惕次谐波振荡

次谐波振荡是电流模式控制的一种固有不稳定性,表现为开关波形宽窄脉冲交替,频率减半,常伴随噪声。

峰值电流模式 PCMC 常用于 Buck 变换器或类似控制器的 Buck 模式。其控制机制是时钟开启 MOSFET,当电感电流上升到预设峰值时关断。

无补偿时,当占空比 D > 0.5,电感电流扰动容易被后续周期放大,从而触发次谐波振荡。

谷值电流模式 VCMC 常用于 Boost 变换器。其控制机制是时钟关断 MOSFET,或由固定导通时间决定,当电感电流下降到预设谷值时重新开启。

它的不稳定条件与 PCMC 相反,无补偿时在 D < 0.5 更容易触发。

通用解决方案是斜坡补偿:在电流采样信号上叠加一个与开关时钟同步的人工斜坡,修正控制环路看到的电流斜率,让微小扰动在后续周期衰减。

现代控制器通常内置自适应斜坡补偿,但设计时仍要理解它和 Buck/Boost 工况的关系。

三、PCB 布局决定波形能不能真正干净

如果器件参数足够、驱动也合理,但 Vgs 振铃、Vds 尖峰、输出纹波尖峰仍然很明显,问题大概率在 PCB 寄生参数。

大功率开关电源的布局核心不是“线够粗”这么简单,而是识别高频电流环路,并把高 di/dt 热环路面积压到最小。

1. 先识别热环路

所有 PCB 布局策略的基础,是对高频电流路径的精确识别。

电流总是以环路形式流动,任何时变电流环路都会产生时变磁场,进而形成辐射。辐射强度与环路面积、电流变化率 di/dt 以及高频分量有关。

因此,最小化高 di/dt 电流环路面积,是抑制 EMI 的根本手段。

不同模式下的热环路重点不同:

| 拓扑/模式 | 热环路位置 | 说明 |

|---|---|---|

| Buck | 输入环路 | 由输入高频电容、上管、下管及其互连构成 |

| Boost | 输出环路 | 由功率开关、整流器或同步管、输出高频电容及其互连构成 |

| 四开关 Buck-Boost | 输入侧和输出侧都存在 | 不能只顾输入侧,也不能只顾输出侧 |

2. 第一步:元件布局先压缩寄生参数

热环路元件优先级最高。高频陶瓷电容和功率 MOSFET 应放在同一层,并尽可能紧凑。

电容焊盘要直接靠近开关器件电源和地引脚,降低环路电感。

元件摆放的重点是:电感应靠近 SW 节点放置,以缩短高 dv/dt 铜皮长度;大容量 Bulk 电容放在高频陶瓷电容外侧;控制器应靠近驱动的功率开关,以缩短栅极驱动路径;FB、COMP 等敏感模拟引脚要远离电感和 SW 节点。

3. 第二步:功率层布线要区分热环路和直流大电流路径

热环路应使用短而宽的铜皮连接,尽量在同一平面内闭合,避免通过过孔换层。

过孔会引入寄生电感,在高 di/dt 下产生电压尖峰,也会破坏参考平面的回流路径。

SW 节点是主要 dv/dt 噪声源。铜皮面积满足载流即可,不应盲目做大。把 SW 节点做得很大,可能降低一点电阻,却会显著增加对周围信号的容性耦合和辐射。

Vin、Vout、PGND 等直流或缓变大电流路径可以使用大量过孔连接多层铜皮,降低阻抗并改善散热。

这类路径的核心矛盾是低阻抗和载流能力,不是像热环路那样严格禁止换层。

4. 第三步:接地架构要保证参考点干净

PGND 是大电流回流路径,必须是低阻抗连续平面。

建议在功率级元件下方设置完整、无分割的接地层,尤其是热环路下方的核心区域,尽量不要让非 GND 网络的过孔破坏回流路径。

AGND 是反馈和补偿网络的参考地,需要稳定的电位基准。模拟部分可以创建独立局部接地敷铜,再通过单点连接汇入 PGND。

常见连接位置是控制器裸露焊盘或输出电容较安静的地端。这样可以减少 PGND 噪声电流流入 AGND,避免影响 FB、COMP 和电流采样。

5. 第四步:关键信号布线保证信号完整性

关键信号不要只按“走得通”处理,而要按信号完整性处理。

FB 分压电阻应紧靠 IC 的 FB 引脚放置。FB 走线要短,远离 SW、电感和栅极驱动线;如果条件允许,可在内层布线,并利用上下相邻接地层屏蔽。

电流采样 CS 应采用 Kelvin 连接,从采样电阻焊盘内侧直接引出差分对到 IC 引脚,避免大电流路径压降混入采样信号。差分线应紧密平行,路径尽量对称。

栅极驱动回路也要按回路看。低边驱动回路为 LGATE 引脚、下管栅极、下管源极、PGND、IC 地,路径要短而宽;高边驱动是浮动回路,自举电容、UGATE、上管栅极、上管源极、SW 节点和自举电容共同构成闭合路径。UGATE 与其返回路径 SW 应短、宽、紧密并行布线,以降低驱动回路寄生电感。

高边驱动布局里,UGATE 靠近 SW 并不一定是坏事。

SW 是高 dv/dt 节点,但 MOSFET 真正关心的是 Vgs,也就是 UGATE 与 SW 的差值。让去路和回路紧密并行,可以利用共模耦合减少差模干扰,同时降低环路电感。

这是高边驱动布局中很重要的取舍。

四、效率分析要拆开损耗来源

电源效率曲线通常先升后降:轻载时,输出功率很小,但控制器功耗、驱动损耗、偏置损耗等固定损耗已经存在,所以效率低;中载时,固定损耗被摊薄,效率达到峰值;重载时,MOSFET、电感、PCB 和采样电阻的 I²R 损耗快速上升,效率开始下降。

1. 固定损耗和负载电流关系较弱

固定损耗包括控制器自身功耗、栅极驱动损耗、偏置损耗以及一部分开关损耗。

控制器为了维持基准、逻辑和驱动功能会持续消耗功率;驱动器每个周期都要给 MOSFET 输入电容充放电;MOSFET 开关瞬间存在电压和电流交越,也会产生开关损耗。

栅极驱动损耗可用以下形式理解:

$$

P_{drive}\approx Q_g\times V_{drv}\times f_{sw}

$$

这说明高频下 Qg 不能忽略,低 Rds(on) 但 Qg 很大的 MOSFET 未必效率更好。

2. 可变损耗主要遵循 I²R

可变损耗主要是传导损耗,与负载电流密切相关,普遍遵循 I²R 规律。

MOSFET 导通损耗为:

$$

P_{cond}=I_{RMS}^2\times R_{ds(on)}

$$

电感 DCR 损耗为:

$$

P_{DCR}=I_L^2\times DCR

$$

PCB 走线、过孔、连接器和采样电阻也会产生类似的电阻损耗。

进入重载区后,这类损耗以电流平方增长,通常成为效率下降的主因。

3. 高电压带来的损耗机制不同于大电流

高电压和高电流一样会增加损耗,但机制不同。

电压越高,开关过程中的电压电流交越损耗越明显,Coss/Eoss 相关损耗越大,体二极管反向恢复损耗也更严重。控制芯片内部 LDO 若从高输入电压降压供电,也会增加自身发热。

耐压更高的 MOSFET 往往 Rds(on) 和寄生电容也更大,这会间接增加导通损耗和开关损耗。

因此耐压不是越高越好,而是要在尖峰裕量和器件损耗之间平衡。

| 损耗驱动因素 | 大电流 | 高电压 |

|---|---|---|

| 核心损耗机制 | 导通损耗 | 开关损耗、Coss/Eoss、反向恢复 |

| 关键关系 | P = I²R | 与 V、V²、Qrr、Eoss 有关 |

| 主要影响部件 | MOSFET、电感、PCB、采样电阻 | MOSFET 寄生电容、体二极管、驱动和偏置 |

| 主导区间 | 重载 | 全负载范围随电压升高加剧 |

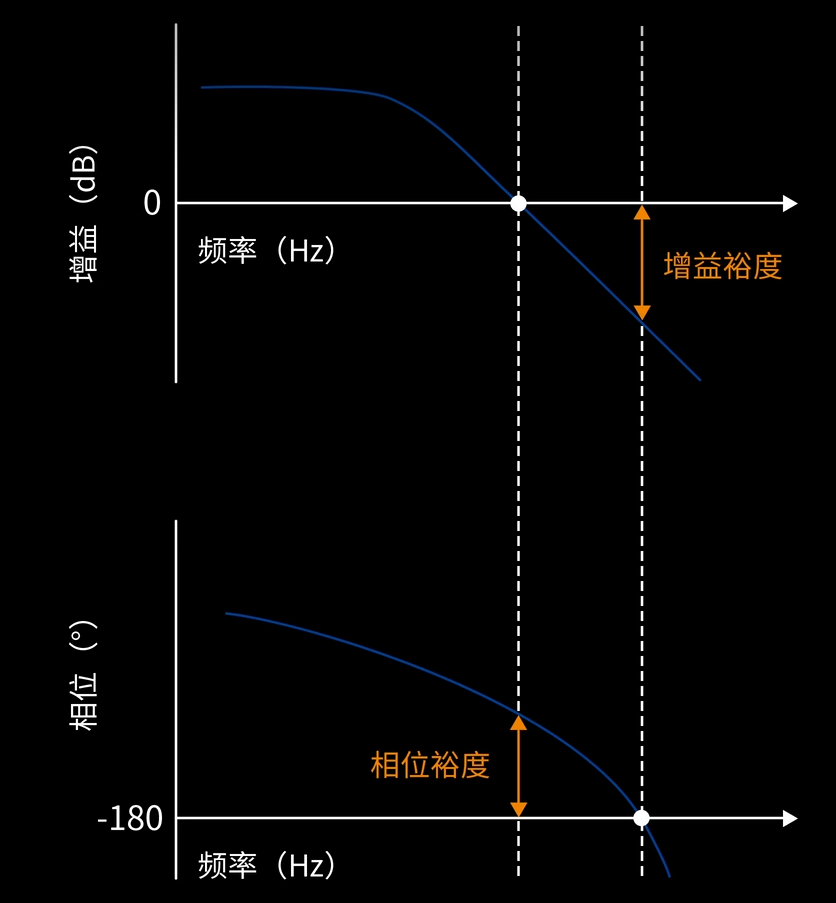

五、环路补偿必须和动态测试一起看

功率级、器件和 PCB 决定了系统的硬件基础,但输出能不能在负载变化时快速稳定,还要看环路补偿。

环路补偿不是孤立计算,而要结合负载瞬态、输出纹波、COMP/FB 波形和波特图一起判断。

1. 电感啸叫往往是环路问题的外在表现

电感或陶瓷电容发出的啸叫,物理上可能来自磁致伸缩或逆压电效应;电气根源通常是轻载下进入可闻频率范围的振荡、间歇工作模式或补偿不足。

诊断时先观察三个现象:输出电压是否低频抖动,开关脉宽是否周期性变化,负载瞬态后是否持续振荡。

然后看 COMP/FB 引脚电压是否稳定,也可以临时在 COMP 与地之间并联 0.1uF 左右电容强制降低环路带宽。

如果异常明显消失,基本可以判断与补偿有关。最终应通过网络分析仪测量波特图,关注相位裕度和增益裕度。

2. 先理解三个波特图指标

| 指标 | 含义 | 工程判断 |

|---|---|---|

| 穿越频率 | 开环增益降到 0dB 的频率点,代表系统响应速度 | 越高动态响应越快,但更容易引入高频噪声和相位不足 |

| 相位裕度 | 在穿越频率处,系统相位距离 -180° 还有多少 | 通常希望大于 45°,常见目标是 45° 到 60° |

| 增益裕度 | 在相位到 -180° 时,增益距离 0dB 还有多少 | 通常希望大于 10dB,用来衡量参数漂移容忍度 |

相位裕度不足时,负载突变后容易出现明显超调和振铃。

3. 用零点和极点理解补偿网络

极点会让增益曲线向下折,斜率降低 20dB/dec,同时带来相位滞后。

零点会让增益曲线向上折,斜率增加 20dB/dec,同时带来相位超前。

原点极点相当于纯积分器,能提供很高的低频增益以消除稳态误差,但会先带来 90° 相位滞后。

三类补偿可以这样理解:

| 类型 | 结构特点 | 主要作用 | 常见搭配 |

|---|---|---|---|

| Type I | 纯积分型,只有原点极点 | 提高低频增益、消除稳态误差,但不能提供相位提升 | 很少单独用于现代高频开关电源 |

| Type II | PI 型,包含原点极点、一个零点和一个高频极点 | 中频处零点把相位拉起来,高频极点压低噪声 | 常用于峰值电流模式控制 |

| Type III | 包含原点极点、两个零点和两个高频极点 | 两个零点提供更强相位提升 | 常用于电压模式控制 |

Type II 理论上最大相位提升约 90°。Type III 理论上最大可接近 180°,适合补偿电压模式下 LC 滤波器的完整双极点系统。

| 特性 | Type I | Type II | Type III |

|---|---|---|---|

| 零极点数量 | 1 极点,0 零点 | 2 极点,1 零点 | 3 极点,2 零点 |

| 最大相位提升 | 0° | 约 90° | 约 180° |

| 主要作用 | 消除直流误差 | 补偿单极点延迟 | 补偿双极点严重延迟 |

| 常见搭配 | 很少单独使用 | 峰值电流模式 | 电压模式控制 |

4. 动态负载测试是环路判断的实操入口

测试不是单独动作,而是验证前面所有设计判断是否成立。

推荐顺序是:低压限流上电 → 看驱动 → 看 SW/Vds → 看电感电流 → 看输出纹波和负载瞬态 → 做温升和效率。

电子负载设置为动态模式。若最大输出电流为 15A,可让电流在 25% 到 75% 之间跳变,例如 3A 到 12A,跳变频率设置在 100Hz 左右,给系统留足恢复时间。

对于 1000W 目标功率,电流阶跃幅度要按真实额定电流重新设置,同时注意电子负载功率、线缆压降和输入电源限流。

四开关 Buck-Boost 的测试重点应放在 Boost 模式下,例如最低输入、满载输出。Boost 模式存在右半平面零点,相位延迟更严重,是环路最容易失稳的恶劣工况。

示波器触发设置也要注意:只用 Vout 触发时,容易被开关纹波误触发;示波器应设置为 AC 耦合、20MHz 带宽限制,并使用 Normal 或 Single 触发模式;加载测试时选择下降沿触发,将触发电平设在稳态纹波谷底之外。

例如稳态纹波最低点为 -30mV,则触发电平可设为 -50mV。这样只有真正的负载跌落会触发。

5. 从瞬态波形反推补偿方向

瞬态波形可以直接反推补偿方向:

| 现象 | 常见判断 | 调整方向 |

|---|---|---|

| 负载阶跃后电压跌落很深、恢复很慢 | 穿越频率太低,动态响应不足 | 适当增大补偿电阻 Rc,把穿越频率往高频推 |

| 恢复过程中有两三个以上明显振铃 | 相位裕度不足,系统欠阻尼 | 尝试增大补偿电容 Cc,降低补偿零点频率,增加穿越频率处的相位裕度 |

| 阶跃后有 1 到 2 个轻微过冲,然后迅速拉平 | 较理想状态 | 通常对应相位裕度大致在 45° 到 60° 的工程范围 |

每次调整补偿后,都应重新观察负载瞬态、输出纹波和 COMP 波形,不能只调一次参数就下结论。

六、面试表达:把技术内容串成一条线

如果面试中被问到四开关 Buck-Boost 的器件选型和调试,可以先给出总体方法,再展开细节。

比较清楚的表达是:我不是只按标称功率选器件,而是先锁定最恶劣工况,再做电压、电流、热和高频损耗降额,最后通过波形、温升、效率和负载瞬态验证。

1. 控制 IC 怎么说

宽压大功率 Buck-Boost 需要同步四开关控制、足够的驱动能力、可靠限流、斜坡补偿和完善保护。

开关频率要在体积、效率、动态响应之间折中。

2. MOSFET 怎么说

MOSFET 可以从三个维度回答:第一是耐压裕量,56V 系统通常不建议直接用 60V 管,工程上会考虑 80V 或 100V;第二是电流和高温降额,低压 Boost 满载时输入电流和峰值电流很高,不能只按平均电流选;第三是损耗权衡,300kHz 下不能只追低 Rds(on),还要看 Qg、Qoss、Coss、SOA 和封装热阻。

3. 电感怎么说

四开关 Buck-Boost 必须分别计算 Buck 和 Boost 两端最恶劣工况,取更大的感值,并保证 Isat 高于逐周期限流阈值,Irms 和 DCR 满足温升和效率要求。

低压 Boost 满载通常是电感电流最严苛的工况。

4. 电容怎么说

输入输出压力不同:Buck 模式输入电容承受较大 RMS 纹波电流,Boost 模式输出电容承受较大 RMS 纹波电流和 ESR/ESL 尖峰。

高频 MLCC 必须贴近热环路,大电容放远只能补能量,不能抑制高频尖峰。

5. 调试怎么说

调试可以按顺序说:先低压限流上电,看 Vgs 是否干净,再看 Vds/SW 的尖峰和振铃,然后看电感电流、输出纹波、负载瞬态、温升和效率。

环路补偿不能凭感觉调,要结合瞬态波形和波特图判断穿越频率、相位裕度和增益裕度。

这条表达线的好处是从设计边界出发,经过器件、布局、波形和环路验证,最后回到工程结果。

它比单独背公式更能说明你真的理解 Buck-Boost 大功率电源的完整设计闭环。

Hacklink panel ile link profilinizi çeşitlendirin. Forum, blog, haber sitesi ve dizin backlinkleri tek çatı altında. 9949